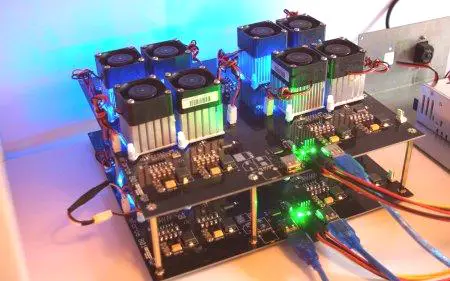

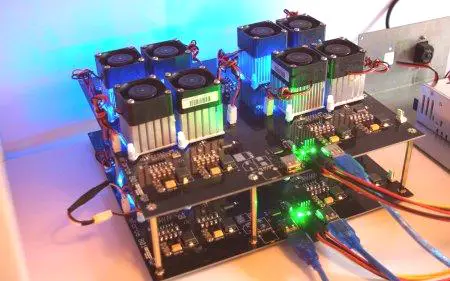

FPGA (FPGA) je skratka pre "Field Programmable Gate Array", a je obrovská pole brány, ktoré môžu byť naprogramované a prestaval v každej dobe a na každom mieste. Mnoho ľudí stále ešte nechápu, čo FPGA. "Obrovská sada brán" - zjednodušený opis modelu. Niektorí FPGA s vloženými tvrdými blokmi, radiče pamäte, vysokorýchlostné komunikačné rozhranie a koncové body PCIe. Vnútri mnohých brán FPGA, ktoré možno ľubovoľne pripojiť k sebe. Princíp viac či menej podobné pripájanie jednotlivých okruhov logické prvky. FPGA vyrába popredných spoločností na svete Xilinx, Altera a Microsemi.

História FPGA

Priemysel rástol FPGA s programovateľným PROM trvalej pamäte a logické zariadenia PLD. V roku 1970 Philips vynašiel Field Programmable matice. Konštrukcia týchto FPGA, skladajúci sa z dvoch plánov dosiahne konkrétnu implementáciu logiku, funkčné káblové pripojenie "A" alebo "ALEBO". To jej dal možnosť realizovať funkcie ako súčet produkcie.

Altera bola založená v roku 1983, a v roku 1984 vydala prvý v priemysle, ktoré môžu preprogramovať logickej jednotky - EP300 s kryštálovým oknom v balení, ktoré nám umožnil použitie UV lampy matricu, aby sa odstránili EPROM štítok. Na prekonanie problémov spojených nákladov a rýchlosti, bol vyvinutý programovateľné logické polia, ktorá obsahovala iba jeden programovateľný "A", ktorá bola zavedená do pevných "alebo" brány. PAL aPLA spolu s ďalšími variantmi sú zoskupené ako jednoduché programovateľné logické zariadenia SPLD. Takéto FPGA, integrované do jedného čipu s poskytnutými prepojeniami pre softvérové pripojenie blokov, sa použili na uspokojenie rastúcich technologických požiadaviek. Oni sú nazývaní integrované PLD a vyvinuté spoločnosťou Altera.

Tranzistory - ďalšia trieda elektronických zariadení založená na programovateľných maskách hradlových polí. Pozostávajú z tranzistorových polí, ktoré možno pripojiť pomocou užívateľských drôtov. Ustúpili do logických blokov a teraz ich užívateľ môže naladiť na mieste, nie vo výrobnom laboratóriu. Myšlienka vývoja prvej komerčne životaschopnej FPGA patrí spoluzakladateľom Xilinx Ross Freeman a Bernard Wondershmitt. XC2064 bol vynájdený v roku 1985 a pozostával zo 64 prispôsobiteľných logických blokov s 3 referenčnými tabuľkami. Poskytuje moderné pochopenie toho, čo je FPGA. Koncom roka 1980 sa experiment Stevea Casselmana v oblasti počítačovej tvorby s 600 000 preprogramovanými bránami našiel sponzorov v námornom vojenskom oddelení námorníctva USA a potom dostal patent v roku 1992.

Do konca roka 1990 došlo k veľkej konkurencii vo výrobe FPGA, potom podiel Xilinxu na trhu začal klesať. Prehrávače ako Actel, Altera, Lattice, QuickLogic, Cypress, Lucent a SiliconBlue získali svoje miesto na celosvetovom trhu FPGA spolu s Xilinxom. V roku 1997 sa Adrian Thompson podaril spojiť programovanie FPGA a technológie genetického algoritmu s FPGA, začínajúc novú éru Evolvable.

Dnes je FPGA dostatočne dostatočnáprístupné, v súvislosti s ktorými sa stále zvyšuje popularita na spotrebiteľských trhoch. Pozostávajú zo súboru logických buniek nazývaných vyhľadávacie tabuľky LUT obklopené prepojenou sieťou, ktorá poskytuje flexibilný systém, ktorý môže implementovať prakticky akýkoľvek digitálny algoritmus.

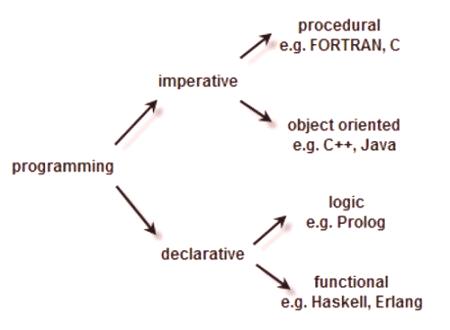

Principy programovania

Programovanie FPGA pre začiatočníkov je proces štúdia, plánovania, navrhovania a implementácie riešenia na FPGA. Počet a typ plánovania sa líši od programu po program. Vytvorenie dokumentu s požiadavkami a vytvorenie návrhu dokumentu vysvetľujúce, ako bude navrhované riešenie implementované, môže byť veľmi užitočné pri riešení potenciálnych problémov.

Čas strávený na vytvorení kvalitného dokumentu projektu ho v budúcnosti zachráni pri refaktoringu, odstraňovaní chýb a opravách chýb. Implementácia programovacieho riešenia FPGA zahŕňa navrhovanie projektu pomocou jednej z metód implementácie projektu. Medzi nimi sú schémy alebo kód HDL, ako Verilog alebo VHDL. FPGA môže naprogramovať zdrojový súbor na fyzické zariadenie FPGA pomocou programovacích nástrojov FTP Altera. Zavedenie dizajnu s využitím schém už nie je v priemysle využívané. Syntéza a programovanie sa takmer úplne starali o nástroje predajcu, ako sú konfiguračné nástroje ISE a Vivado a laboratórium Numato Lab.

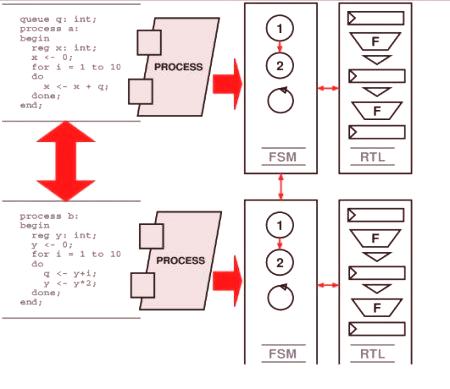

Rýchlosť prenosu RTL

RTL udáva prenosovú rýchlosť registra. Vývojár sa tiež môže stretnúť s podmienkami Register Logic Transfer alebo Register Transfer Language, to všetko znamenáto isté, čo sa týka dizajnu zariadení. RTL je abstrakcia vyššej úrovne pre návrh digitálneho hardvéru, ktorá sa nachádza niekde medzi striktnou behaviorálnou simuláciou na jednom konci a čisto štrukturálnou na úrovni brány - na druhej strane. Simulácia brány znamená opis hardvéru s použitím základných ventilov, ktorý je dosť oslabujúci. RTL možno považovať za analóg termínu "pseudokód" použitý v programovacom rámci FPGA. Návrh hardvéru môžete opísať ako postupnosť krokov alebo dátových tokov z jednej sady registrov do druhej v každom cykle hodín. RTL sa tiež nazýva dizajn "dátového toku". Akonáhle je projekt RTL pripravený, je ľahšie ho zmeniť na skutočný kód HDL pomocou jazykov ako Verilog, VHDL, SystemVerilog alebo akýkoľvek iný hardvérový jazyk. FPGA je oveľa viac než len sada brán. Hoci je možné vytvoriť logické schémy akejkoľvek zložitosti, organizovať a spájať logické prvky. Je to spôsob, ako vyjadriť logiku v jednoduchom formáte, ktorý sa môže nakoniec premeniť na pole prvkov. Dve populárne spôsoby, ako to urobiť, sú: zavedenie schémy a jazykového popisu vybavenia HDL. Predtým, ako sa to široko používalo, inžinieri navrhli všetko prostredníctvom schém. Boli veľmi jednoduché pri malých projektoch, ale bolestivo nekontrolované - pre tie veľké. Len si predstavte, ako inžinieri Intel nakresli obvod pre Pentium s miliónmi brán! Je neprijateľne ťažké.

Verilog je opis hardvéru HDL, ktorý môžete použiťdigitálne obvody v obyčajnom texte. Učenie Verilog nie je také ťažké, ak používateľ má skúsenosti s programovaním. VHDL je ďalší populárny HDL, ktorý je v priemysle široko používaný. Verilog a VHDL majú viac alebo menej rovnaké uznanie na trhu, ale používatelia zvyčajne vyberajú Verilog, pretože je ľahké sa naučiť a má syntaktickú podobnosť s jazykom C.

Programovacie technológie

FPGA môžu byť považované za stavebné bloky, ktoré umožňujú správne nastavenie zariadenia. Toto je špeciálna forma PLD s vyššou hustotou a rozšírenými funkciami v kratšom časovom rámci pomocou CAD. FPGA sú k dispozícii v rôznych verziách založených na používanej programovacej technológii. Môžu byť naprogramované pomocou:

Antifuse Technology. Programovanie založené na technológii zariadenia Flash od firmy Actel. FPGA môže byť preprogramovaná niekoľko tisíckrát, čo trvá niekoľko minút v samotnom poli pre preprogramovanie a má trvalú pamäť.FPGA založená na SRAM, ktorá ponúka neobmedzené preprogramovanie a veľmi rýchlu rekonfiguráciu alebo čiastočnú rekonfiguráciu počas samotnej práce s malým počtom ďalších obvodov. Väčšina z týchto spoločností, ako napríklad Altera, Actel, Atmel a Xilinx, vyrába tieto zariadenia.

Konfigurované logické bloky

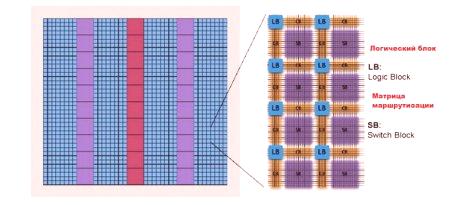

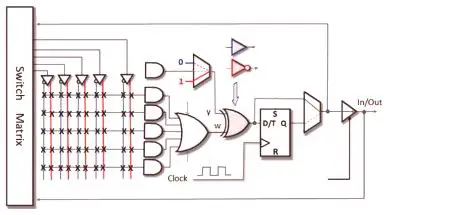

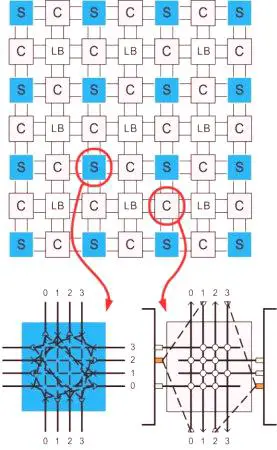

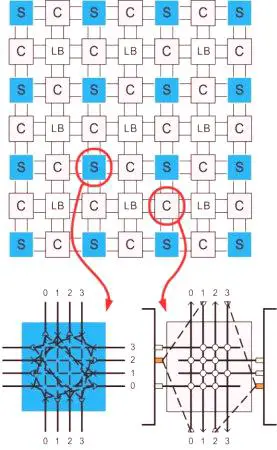

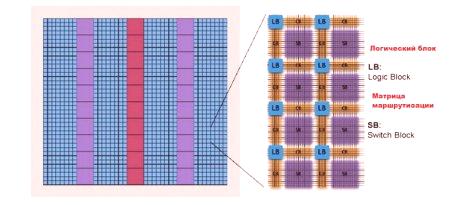

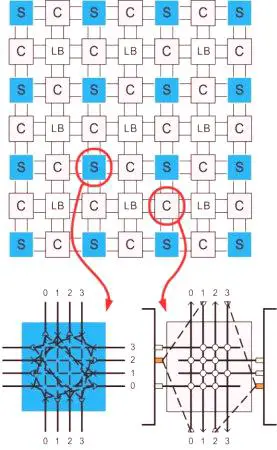

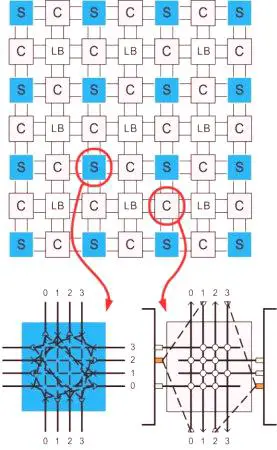

Bez ohľadu na rôznych výrobcov a niekoľko rôznych architektúr a funkčných množín má väčšina FPGA spoločný prístup. Hlavné bloky komponenty akéhokoľvek FPGA sú flexibilné programovateľné "logické bloky" (CLB), obklopené programovateľnými "blokmiI /O "s hierarchiou smerovacích kanálov, ktoré spájajú rôzne bloky na doske.

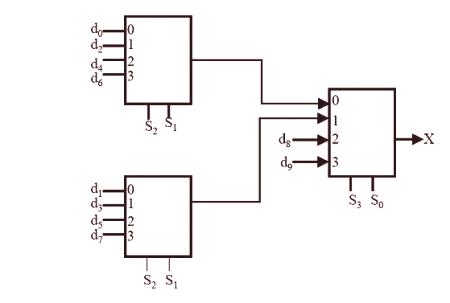

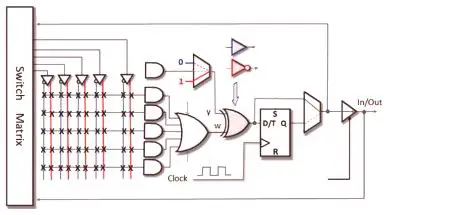

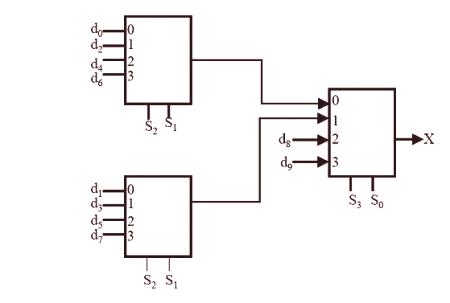

Okrem toho môžu obsahovať súbory DLL na priradenie a riadenie hodín a pamäte RAM vybraného bloku s hlavným stavebným blokom logickej bunky. Posledný z nich pozostáva z generátora vstupných funkcií, logiky prenosu a ukladania prvkov. Generátory sú implementované vo forme referenčných tabuliek a závisia od vstupu. Napríklad Xilinx Spartan II má 4 vstupné LUTs, ktoré poskytujú každú 16X1-bitovú synchrónnu RAM s použitím multiplexorov ako posuvných registrov na zachytenie dát v dávkovom režime. Úložné prvky sú citlivé na okraje spúšťačov alebo na úroveň zámkov. Fragmentácia FPGA:

Aritmetická logika zahŕňa bránu XOR, ktorá pracuje s plným sčítačom a prideľuje logické prenosové linky. Block I /O a matica smerovania. Táto jednotka má vstupy a výstupy, ktoré podporujú širokú škálu štandardov a rozhraní pre signalizáciu.Základný I /O blok je zobrazený nižšie. Pufr pod vstupnými a výstupnými cestami vysiela signály do vnútornej logiky a konečnej platformy priamo alebo cez spúšť. Sú konfigurované tak, aby spĺňali rôzne podporované štandardy alarmu, ktoré môžu byť definované používateľom a inštalované zvonku.

Routing Matrix

Na ľubovoľnej montážnej linke pomalý segment určuje celkový výkon. Smerovacie algoritmy sa používajú na vývoj najefektívnejších spôsobovzabezpečenie optimálneho výkonu. Smerovanie sa vykonáva na rôznych úrovniach, ako je miestna, smerovacie účelu medzi CLB, smerovanie IO medzi blokmi a CLB, venovanej smerovanie pre určité triedy signálu, aby sa maximalizovala produktivita a globálne smerovanie distribúcie hodiny a ďalšie signály s veľmi veľkým rozvetvenie , Rodiny majú tiež veľký FPGA blok RAM štruktúry pre doplnenie distribuované LUT RAM, ktorej veľkosť sa mení pre rôzne zariadenia FPGA.

Vyhotovenie FPGA poskytuje v podstate rovnaký prístup ako každého systému VLSI, fázy, ktoré sú konštrukcie, modelovanie správania, syntéza, simulácie po syntéze, preklady, mapovanie a smerovanie, a ďalšia analýza, ako je napríklad synchronizácia modelovacej a statickú synchronizačnú analýzu. Počítač dizajn vyzerá riadny a položil tašku, ale v skutočnosti je nedokonalá umiestnenie a smerovanie, čo znižuje produktivitu. Vždy môžete použiť viac tranzistorov na zvýšenie výkonu FPGA. Oblasť služieb je vysoká. Inštalácia viacerých tranzistorov znamená, že sú možné veľké projekty. Únik je vážny problém pre FPGA a zároveň je zaujímavý. Asynchrónne FPGA architektúra vykazuje lepšie výsledky v kombinácii s reťazovým procesným technológiu, ktorá znižuje globálne vstupy a zvyšuje priepustnosť.

Otázky kvality a hradieb

Bezpečnosť systému bola vždyhlavný problém, pretože kód by mal byť otvorený zakaždým, keď je načítaný do FPGA. Táto flexibilita spôsobuje, že FPGA predstavuje potenciálnu hrozbu pre zlomyseľné zmeny vo výrobnom procese, takže šifrovanie bitových prúdov sa dostalo na pomoc včas. Často neskúsení dizajnéri a užívatelia sú konfrontovaní s dilemou o tom, aký silný je FPGA pre ich vývoj. Výrobcovia často uvádzajú metriky, napríklad "počet brán". Napríklad, programovanie FPGA Xilinx používa tri metriky pre meranie objemu FPGA, maximálna logických prvkov, maximálna bitov pamäte a typický rozsah brán. Tak dlho, kým sú konzistentné, migrácia medzi modelmi je trochu zjednodušené, ale len zriedka poskytuje presné porovnanie rôznych predajcov prostredníctvom rôznych architektúry a pretože rozdielov vo výkonnosti. Najlepším ukazovateľom je porovnať typ a množstvo poskytnutých logických zdrojov. Okrem toho musí vývojár plne pochopiť, čo presne sa od zariadenia vyžaduje, pretože výrobcovia sa môžu pochváliť funkciami, ktoré budú najmenej dôležité pre prácu. Napríklad Stratix II EP2S180 z Altera má asi 186.576 LUT so 4 vstupmi a Xilinx Virtex-4 obsahuje XC4VLX200 podľa 178176. Avšak, v prípade, že konštrukcia vyžaduje len 177.000. LUT, bude stačiť.

Ak je RAM - žiaduce metrika pre návrhárov, ani Xilinx XC4VLX200 6 Mbps alebo 9 Mbps Altera EP2S180 nie je lepšie, v porovnaní s menej ako inzerovanej, staršieho modelu XC4VFX140 99 Mbps.

Programovacie jazyky a softvér

Programovanie FPGA Altera pre začiatočníkov začína výberom jazyka. Možnosť C, C ++ aleboSystém C vám umožňuje využívať možnosti najväčších zariadení a zároveň dosiahnuť podobnosť realistickej vývojovej grafiky. Schopnosť používať dizajnu FPGA C-založený poskytovanej HLS (High Level Synthesis), ktorá po mnoho rokov je na pokraji prielomu nástroje, ako je kľučka-C. V poslednej dobe sa stala realitou, pretože hlavné dodávatelia Altera a Xilinx ponuka HLS vo svojej toolbox Spectra-Q a Vivado HLX resp. K dispozícii niekoľko ďalších implementáciách Altera FPGA programovanie pre začiatočníkov až C, napríklad na OpenCL, ktorý je určený pre softvérových vývojárov, ktorí chcú zvýšiť výkon použitím FPGA bez hlbokej znalosti FPGA. Rovnako ako u HDL, HLS je obmedzená na prístupy využívajúce programovanie FPGA v jazyku C, ako u tradičného HDL, vývojári pracovať s podmnožinou jazyka. Napríklad je ťažké syntetizovať a realizovať systémové volania v prípade potreby zabezpečiť, aby všetky obmedzené a má pevnú veľkosť. V HLS Nice, ktoré si môžete navrhnúť svoje algoritmy s plávajúcou desatinnou čiarkou a nástroja je HLS konverzia plávajúcou desatinnou čiarkou na fixné. Programovanie FPGA s Xilinxom nie je vôbec ťažké. Môžete si ho zakúpiť zakúpením produktov Xilinx zadarmo alebo podľa cenovo špecifického modelu. Môžete pristupovať k videu na stránke profilu, čo jasne ukazuje postup používania. Zo všetkých spoločností, ktoré sa dajú vybrať pri hľadaní programovateľných polí, je Xilinx rozhodne najlepším zo všetkých. Sú to tvorcovia tohto produktu a ajmnoho rokov ho zlepšilo. Firmvér sa stal silnejším ako kedykoľvek predtým.

Štádiá návrhu

Programovanie FPGA sa môže vykonávať online, pretože platforma je dobre prezentovaná na internete. Pri nastavení FPGA je prvým krokom navrhnutie okruhu, pre ktorý sú potrebné znalosti digitálnej elektroniky. Na rozdiel od programovania je oveľa ťažšie začať rezať kód, ak architektúra programu nie je jasná. Akonáhle je jasné, že je potrebné implementovať, začnite opísať schému pomocou jedného z jazykov: Verilog alebo VHDL. Skutočnosť, že sa paradigma mení, je, že sa nenazývajú programovacími jazykmi FPGA, ale sú to jazyky popisu. Z dôvodu zložitosti testovania digitálnych obvodov je zvyčajne v tomto štádiu banky používať testy, ktoré simulujú správanie zariadení. Tento typ nástroja vám umožňuje kedykoľvek zobraziť stav signálu a skontrolovať, či existujú prechody s požadovanými výsledkami.

Tretia etapa známa ako syntéza schémy je jedným z kľúčov. Vyberá použité prvky a ich vzájomné prepojenia v súlade s popisnými súbormi. V tejto fáze potrebujete nástroje, ktoré vo väčšine situácií zjednodušujú a automatizujú úlohy.

Hardvér a ladenie

Intel Quartus Prime Softvér Suite Lite Edition - softvér na navrhovanie FPGA. Je to ideálne pre začiatočníkov, pretože to môže byť stiahnuté zadarmo a nepotrebujete licenčný súbor. Softvér si môžete stiahnuť na webových stránkach výrobcu. Veľkosť (niekoľko gigabajtov) z nichSťahovanie a inštalácia môže trvať dlho. Ak chcete minimalizovať čas a požadovaný priestor na disku, odporúčame prevziať iba tie položky, ktoré sú potrebné pre vlastné úlohy. Na vyžiadanie súbory na stiahnutie, odstráňte začiarknutie "Select All" a vyberte iba Quartus Prime a podporu pre zariadenie Cyclone V. Algoritmus pre projekt:

Otvorte sprievodcu novým projektom. Zvoľte Next & gt; Katalóg & gt; & gt; Názov objektu najvyššej úrovne.

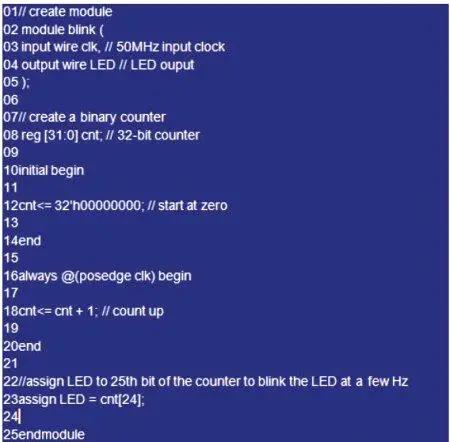

Vyberte adresár pre umiestnenie projektu, napríklad "Blink" a umiestnite ho do priečinka intelFPGA_lite, ale môžete ho umiestniť kamkoľvek a kliknúť na "Next". Po zobrazení výzvy na vytvorenie adresára zvoľte "Áno". Vyberte položku "Empty project" a kliknite na "Next". Pridajte súbory a "Ďalej". Nastavte rodinu, zariadenie a dosku výberom nasledujúceho: rodina - cyklón V, prístroj - cyklón V SE, základňa, názov zariadenia: 5CSEBA6U2317. Ak chcete vybrať konkrétne zariadenie, musíte kliknutím na šípky nahor /nadol zobraziť zoznam podporovaných zariadení, kým sa nezobrazí 5CSEBA6U2317. Užívateľ môže potrebovať rozšíriť pole "Name", aby sa zobrazilo celé meno zariadenia, kliknite na "Next". Pri nastavovaní nástroja EDA sa používajú štandardné nástroje, takže nebudú vykonané žiadne zmeny, kliknite na tlačidlo "Ďalej" a "Hotovo". Zobrazí sa súhrnná obrazovka. Vytvorte súbor HDL so zavedením Verilog ako HDL. Prejdite na kartu Súbor (hlavné okno) a vyberte položku Nový. Vyberte súbor Verilog HDL a kliknite na tlačidlo OK. Vyberte položku Súbor & gt; "Uložiť ako".Vyberte názov súboru. Toto je názov súboru najvyššej úrovne a mal by zodpovedať názvu projektu. Kliknite na tlačidlo "Uložiť". Vytvorte modul Verilog. Skopírujte a vložte kód Verilog do okienka blink.v a uložte kódový súbor.Kliknite pravým tlačidlom myši na položku Analýza a syntéza a potom kliknite na tlačidlo Štart a vykonajte Verilog syntax a overovanie syntézy.Ak sa proces úspešne dokončí spolu s analýzou a syntézou, zobrazí sa zelená značka. Ak sa vyskytne chyba, skontrolujte syntax a uistite sa, že sa presne zhoduje s blokom kódov uvedeným vyššie. Všetci skúsení programátori vedia, že komplexné programy, dokonca aj podprogramy, nefungujú správne po prvýkrát. Abstrakčná schopnosť osoby na základe skúseností mu umožňuje nájsť riešenie bez obáv o najmenšie detaily. Ale prísna pravda je, že fyzický systém, do ktorého je program zapracovaný, si vyžaduje, aby každý malý detail bol zohľadnený skôr, ako to všetko funguje. S vývojom softvérových nástrojov pre vývoj FPGA, najmä od tradičných dodávateľov, ako aj od nezávislých poskytovateľov nástrojov: Synplicity, FPGA - sa stáva čoraz obľúbenejším deň čo deň. Teraz FPGA začala zahŕňať špecializovaný hardvér, aby zákazníkovi poskytol potrebné funkcie, čo znižuje náklady pre výrobcov. Takže v budúcnosti sa v budúcnosti môže objaviť konkurencia medzi tvrdými a lacnými systémami s pružnými jadrami. Očakáva sa, že v blízkej budúcnosti budú náklady znižovať ešte viac kvôli popularite FPGAbude niekedy narastať. Výrobcovia začali experimentovať s koncepciou vloženia FPGA do integrovaných obvodov na vytvorenie hybridného zariadenia. Zameriava sa stále na smerovanie prepojení a menšie zmeny sa zaznamenali v architektúrach CLB. Vzhľadom na to, že FPGA naďalej obsahujú procesory, nová generácia vyžaduje nielen znalosť hardvéru digitálneho dizajnu, ale aj skúsenosti vývojárov v procese jednorazového programovania FPGA. Vo všeobecnosti sa očakáva, že FPGA odoberie trhový podiel v zariadeniach ASIC a stane sa dominantnou technológiou, ktorá bude zahŕňať mnoho aplikácií z rôznych oblastí.